PCなどの情報通信機器、AIやロボティクス、IoT技術を駆使して様々な仕組みを一層便利で豊かなものにする。「超スマート社会」の実現が各方面で研究されている今、デジタルトランスフォーメーションを支える半導体集積回路はますます重要なものとなっている。

各種ICTデバイス・システムには、情報の記憶を担うメモリチップが使用されている。コンピュータに用いられるメモリは、動作速度と容量により階層化されている。ピラミッドの頂点に近づくほど容量は小さくなるが、動作速度は大になる。裾野のそれは遅いが容量大である。ピラミッドの中心領域~頂点付近に用いられる揮発性メモリ(DRAM/SRAM)は、半導体技術の進歩に伴い、容量・速度ともに増加の一途をたどってきた。

その進歩が近ごろ鈍化している。原因の一つは、電源を切っても消費される待機電力の増加にある。上記半導体メモリが揮発性であることに加え、トランジスタの微細化にともなうリーク電流(集積回路内の漏れ電流)の増大に因るものだという。動作していないときにも電力を消費してしまう問題を解決するために、電子の持つ2つの性質(電荷とスピン)を利用するスピントロニクス技術を使った不揮発性メモリが注目されているという。

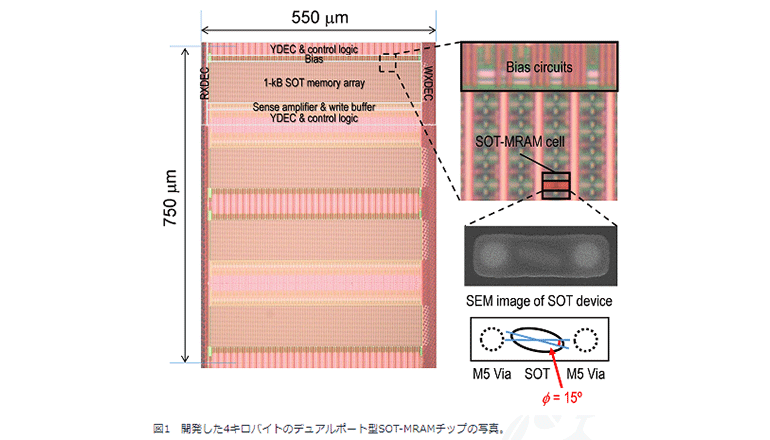

東北大学のCIESと電気通信研究所の研究グループは、スピン軌道トルク型磁気トンネル接合(SOT-MTJ)素子とSi-CMOS技術を組み合わせた集積回路技術によって、高速なデータの読み書きを可能とするデュアルポート型SOT-MRAMチップを試作し、その動作実証に初めて成功した。

今回の不揮発性メモリ技術は、ICT社会基盤のパラダイムシフトをもたらし、Society5.0の基盤技術として期待されるという。内閣府ImPACTならびにCIESコンソーシアムによる上記実験の成果は、集積回路技術に関する世界最高峰の国際会議の一つ「VLSI2020」にて発表された。