東北大学国際集積エレクトロニクス研究開発センター(CIES)の遠藤哲郎センター長(兼 同大学大学院工学研究科教授、先端スピントロニクス研究開発センター副拠点長、省エネルギー・スピントロニクス集積化システムセンター長、スピントロニクス学術連携研究教育センター部門長)の研究グループが成功。

STT-MRAM は、その最初の応用先として混載メモリが最も有望視されている。従来技術である「eFlash」と比べると、STT-MRAMでは、セル面積(メモリ密度)はほぼ同程度であるものの、電源電圧を低減できるために低消費電力化でき、さらに書き換え耐性が高いために信頼性を向上できる。

一方、SRAMと比較するとセル面積が減少できるために高密度化でき、さらに不揮発性により低消費電力化できる。これらのキャッシュアプリケーションなどの混載メモリへの応用を目指す場合には、STT-MRAMの高密度化していく必要がある。これまでの混載メモリ応用を目指したSTT-MRAMの報告では、大手ファウンドリ会社からの報告でも8Mb-40Mbであり、さらなる高密度化が望まれていた。

高密度STT-MRAMを実現するためには、半導体テクノロジーノードの微細化に加えて、STT-MRAM 中で記憶素子として用いられる「MTJ素子」の微細化も必要。今回の研究では、MTJ素子を39ナノメートルまで微細化。さらにメモリセルの構造を工夫し、MTJを集積回路の後工程で作製される「Via」と呼ばれる電極上に作製することで、メモリセルの面積を減少させることに成功した。

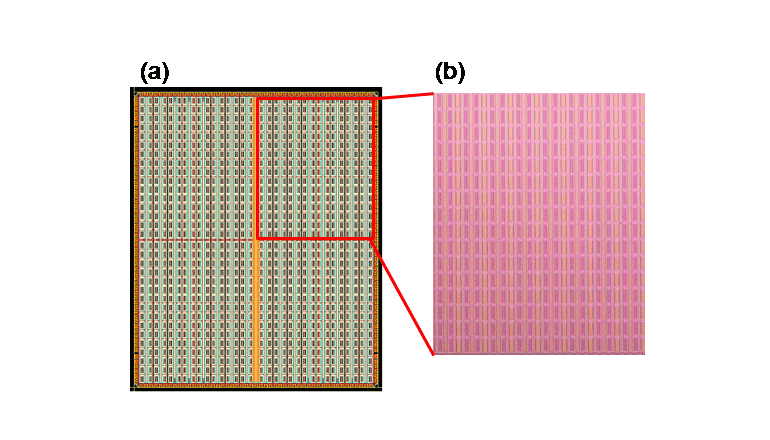

また、同メモリセルを用いて128Mb密度のSTT-MRAMを設計。試作した同STT-MRAMのサブアレイにおいて高速動作特性を評価し、1.2Vという低い電源電圧で14ナノ秒という高速動作の実証に成功した。

今回開発された技術により、大容量(高密度)混載のSTT-MRAM製造への道が切り拓かれ、IoTやAIチップなどに広く用いられるキャッシュアプリケーションなど、STT-MRAM の応用範囲が更に拡がることが期待されるという。