ガラスや金属の内部ひずみを除去する技(焼き鈍し)に由来するアニーリングは、近ごろ量子コンピュータの動作原理として注目されている。交通渋滞の解消など、膨大な要素の複雑な組み合わせから最適解を得る手法として――。

そこで3年前、特殊な冷却装置を要する量子コンピュータに対して、同様の計算を室温下でできる新型半導体コンピュータを試作し、翌年にはその計算規模を10倍にする技術を開発した。日立製作所はきょう、大規模かつ複雑化し続けている社会課題の解決に向けて、より高速でスケーラブルな世界最大級のCMOSアニーリングマシンを開発したと発表した。

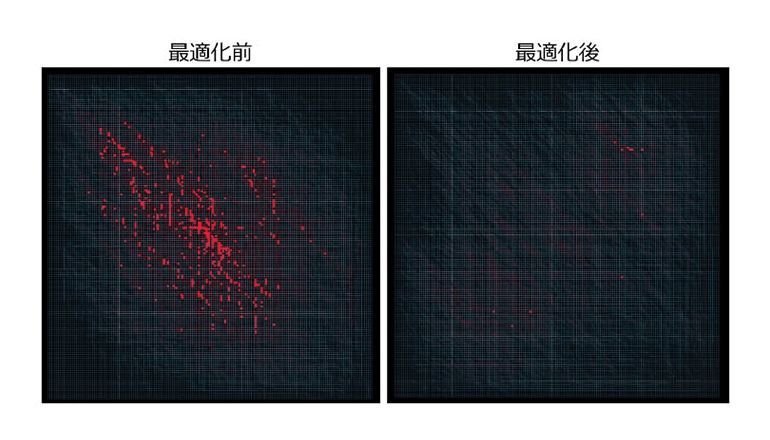

上下2つの向きを示すスピン(格子点)で構成されるイジングモデルについて、それを半導体で模擬してアニーリングを行う。CMOSアニーリングチップ(FPGA)を25枚接続――。102,400パラメータの問題に対応でき、これまで拡張が制限されていたアニーリングマシンの性能を、解放できることを実証した。

チップ間の接続では、高速変化するパラメータを隣接チップに送受信する必要があり、多数接続時に通信量が急増しないことが求められる。一方、各チップ境界部分ではパラメータのみの送受信で十分である。ここに着目し、隣接チップ同士で常時パラメータを送受信させる部分結合型を適用、全体で一つの大規模計算機とした。

全結合型のように接続数と通信量/チップとが比例しない。省電力・低コストで大規模化が可能なチップ25枚によるCMOSアニーリングマシンを用いて、今回、都市の交通渋滞軽減に向けた最短経路探索と並行して、混雑位置を避けるための車両の経路制御をシミュレーションした。結果、従来試作機の25倍の面積、約5k㎡にて、一台当たり数ミリ秒で経路探索処理できることを確認した。

同社は、今回開発したマシンを8月より、最適化問題を課題としているパートナー向けにクラウドサービスとして公開するという。