製造

世界初!5 nmプロセスによる高性能クロック回路を実現

携帯電話、パソコン、テレビなど、多くの電子機器にはLSI(大規模集積回路)が搭載されている。それは、デジタル信号を処理するデジタル回路部と、外部からのアナログ信号を扱うアナログ回路部とで構成される。

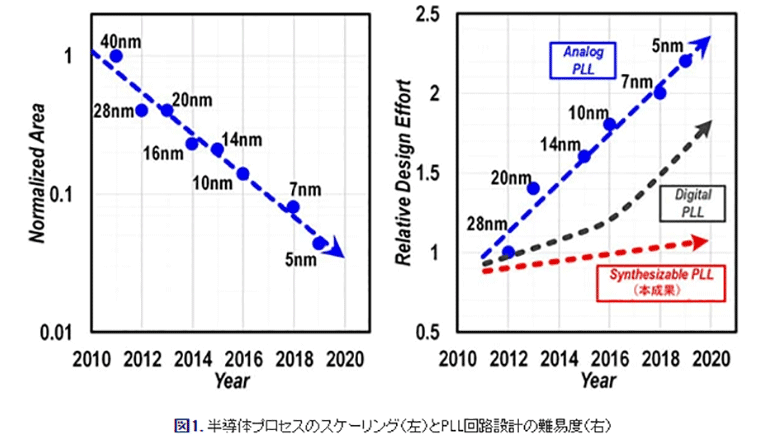

LSIを製造する半導体製造プロセスの微細化にあわせてデジタル回路は小型化・高性能化が可能だが、アナログ回路は小型化が困難であり、微細な製造プロセスほど設計が困難になることが大きな問題になっているという。東京工業大学 工学院ー電気電子系の岡田ラボ、およびソシオネクストの共同研究グループは、最先端の5 nm FinFET CMOSプロセスで世界初となる世界最小の高性能分数分周型クロック回路の開発に成功した。

プロセッサやメモリ、通信用の"時計"で必須となる。PLL(位相同期回路)において、アナログ回路設計で具現化されていたデジタル制御発振器(DCO)と時間差デジタル変換器(TDC)をデジタル回路構成により実現し、集積回路全体をデジタル化した。上記クロック回路は、小型ながらも優れたジッタ特性を持つ。細かい周波数調整が可能な分数分周型PLLで構成されていて、スペクトル拡散クロックの生成ができる――。

従来アナログ回路設計者が時間をかけて設計・チューニングする必要があった。クロック回路は今回開発した技術により、通常のデジタル回路と同様に自動配置配線が可能となり、非常に短時間で所要プロセスやクロック周波数に合わせて最適に設計できる。製造プロセスの微細化にあわせてスケーラブルに回路面積を小型化することも可能となる。

幅広い用途のSoC(システム・オン・チップ)の小型化・低コスト化を達成できるという。技術を開発した上記グループの研究は、テラピクセル・テクノロジーズの協力により実現したものであり、その成果は米国電気電子学会誌「IEEE Solid-State Circuit Letters」に掲載された。